# C-SKY V2 CPU Applications Binary Interface Standards Manual

Release 2.1

csky

## Copyright © 2018 Hangzhou C-SKY MicroSystems Co., Ltd. All rights reserved.

This document is the property of Hangzhou C-SKY MicroSystems Co.,Ltd. This document may only be distributed to: (i) a C-SKY party having a legitimate business need for the information contained herein, or (ii) a non-C-SKY party having a legitimate business need for the information contained herein. No license, expressed or implied, under any patent, copyright or trade secret right is granted or implied by the conveyance of this document. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise without the prior written permission of C-SKY MicroSystems Co.,Ltd.

## Trademarks and Permissions

The C-SKY Logo and all other trademarks indicated as such herein are trademarks of Hangzhou C-SKY MicroSystems Co.,Ltd. All other products or service names are the property of their respective owners.

#### Notice

The purchased products, services and features are stipulated by the contract made between C-SKY and the customer. All or part of the products, services and features described in this document may not be within the purchase scope or the usage scope. Unless otherwise specified in the contract, all statements, information, and recommendations in this document are provided "AS IS" without warranties, guarantees or representations of any kind, either express or implied. The information in this document is subject to change without notice. Every effort has been made in the preparation of this document to ensure accuracy of the contents, but all statements, information, and recommendations in this document do not constitute a warranty of any kind, express or implied.

Hangzhou C-SKY MicroSystems Co.,LTD

Address: 15 Story of Building A, Tiantang software center, XiDouMen road, Xihu district, Hangzhou, China

Post code: 310012

Offical website: www.c-sky.com

# Contents

| 1 | Abo  | ut this Document                                    | 1         |

|---|------|-----------------------------------------------------|-----------|

|   | 1.1  | Abstract                                            | 1         |

|   | 1.2  | Purpose                                             | 1         |

|   | 1.3  | References                                          | 2         |

|   | 1.4  | Current status and anticipated changes              | 2         |

|   | 1.5  | Overview                                            | 3         |

|   |      | 1.5.1 Low-Level Run-Time Binary Interface Standards | 3         |

|   |      | 1.5.2 Object File Binary Interface Standards        | 3         |

|   |      | 1.5.3 Source-Level Standards                        | 3         |

|   |      | 1.5.4 Library Standards                             | 3         |

|   |      | 1.5.5 Change history                                | 3         |

| 2 | Lowe | er-level Binary interfaces                          | 4         |

|   | 2.1  | Processor Architecture                              | 4         |

|   |      | 2.1.1 Control Registers in C-SKY V2.0               | 5         |

|   |      | 2.1.2 Primary Data Type                             | 6         |

|   |      | 2.1.3 Composite Data Type                           | 8         |

|   | 2.2  | Function Calling Convention                         | 9         |

|   |      | 2.2.1 Register Assignments                          | 9         |

|   |      | 2.2.2 Stack Frame Layout                            | 11        |

|   |      | 2.2.3 Argument Passing                              | 12        |

|   |      | 2.2.4 Variable Arguments                            | 13        |

|   |      | 2.2.5 Return Values                                 | 14        |

|   | 2.3  | Runtime Debugging Support                           | 15        |

|   |      | 2.3.1 Function Prologues in C-SKY V2.0              | 15        |

|   |      | 2.3.2 Stack Tracing                                 | 16        |

| 3 | High | language Issures                                    | 17        |

|   | 3.1  | C preprocessor predefinitions                       | 17        |

|   | 3.2  | Inline assembly syntax                              | 17        |

|   |      | 3.2.1 Overview                                      | 17        |

|   |      | 3.2.2 Basic usage                                   | 18        |

|   |      | 3.2.3 Extended asm                                  | 18        |

|   |      | 3.2.4 Examples                                      | 22        |

|   | 3.3  | Name mapping                                        | 24        |

| 4 | ELF  | file format                                         | <b>25</b> |

|   |      |                                                     |           |

|   | 4.1 | ELF Header                           | 25   |

|---|-----|--------------------------------------|------|

|   | 4.2 | Section Layout                       |      |

|   | 1.2 | 4.2.1 Section Alignment              |      |

|   |     | 4.2.2 Section Attributs              |      |

|   |     | 4.2.3 Special Sections               |      |

|   | 4.3 | Symbol Table Format                  |      |

|   | 4.4 | Relocation Information Format        |      |

|   | 4.4 |                                      |      |

|   |     | 4.4.1 Reclocation Fields             |      |

|   | 4 5 | 4.4.2 Relocation Types               |      |

|   | 4.5 | Program Loading                      |      |

|   | 4.6 | Dynamic Linking                      |      |

|   |     | 4.6.1 Dynamic Section                |      |

|   |     | 4.6.2 Global Offset Table            |      |

|   |     | 4.6.3 Function Address               |      |

|   |     | 4.6.4 Procedure Linkage Table        | 47   |

|   | 4.7 | PIC Examples                         | 50   |

|   |     | 4.7.1 Function proglogue for PIC     | 50   |

|   |     | 4.7.2 Date Objects                   |      |

|   |     | 4.7.3 Function Call                  |      |

|   |     | 4.7.4 Branching                      |      |

|   | 4.8 | Debugging Information Format         |      |

|   | 1.0 | 4.8.1 DWARF Register Numbers         |      |

|   |     | Total Dyvilla 100810001 Trainboild   |      |

| 5 | Run | ntime library                        | 56   |

|   | 5.1 | Compiler assisted Libraries          |      |

|   | 5.2 | Floating Point Routines              |      |

|   | J   | 5.2.1 Arithmetic functions           |      |

|   |     | 5.2.2 Conversion functions           |      |

|   |     | 5.2.3 Comparison functions           |      |

|   | 5.3 | Long Long integer Routines           |      |

|   | 0.0 | 5.3.1 Arithmetic functions           |      |

|   |     |                                      |      |

|   |     | 5.3.2 Comparison functions           |      |

|   |     | 5.3.3 Trapping Arithmetic Functions  |      |

|   |     | 5.3.4 Bit Operations                 | 61   |

| c | A   |                                      | C.C. |

| 6 |     | sembly syntax and directives         | 62   |

|   | 6.1 | Section                              |      |

|   | 6.2 | Input line lengths                   |      |

|   | 6.3 | Syntax                               |      |

|   |     | 6.3.1 Preprocessing                  |      |

|   |     | 6.3.2 Symbols                        |      |

|   |     | 6.3.3 Constants                      | 64   |

|   |     | 6.3.4 Expressions                    | 64   |

|   |     | 6.3.5 Oprators and Precedence        | 64   |

|   |     | 6.3.6 Instruction Memonics           | 65   |

|   |     | 6.3.7 Instruction Arguments          | 65   |

|   | 6.4 | Assembler directives                 | 66   |

|   |     | 6.4.1 .align abs-exp [, abs-exp]     |      |

|   |     | 6.4.2 .ascii "string" {, "string"}   |      |

|   |     | 6.4.3 .asciz "string" {, "string"}   |      |

|   |     | 6.4.4 .byte exp {, exp}              |      |

|   |     | 6.4.5 .comm symbol, length [, align] |      |

|   |     |                                      |      |

|   |     |                                      |      |

|   |     | 6.4.7 double float $\{$ , float $\}$ | 67   |

|     | 6.4.8  | equ symbol, expression              |

|-----|--------|-------------------------------------|

|     | 6.4.9  | .export symbol {, symbol}           |

|     | 6.4.10 | .fill count [, size [, value]]      |

|     | 6.4.11 | .float float {, float}              |

|     | 6.4.12 | .ident "string"                     |

|     | 6.4.13 | .import symbol {, symbol}           |

|     | 6.4.14 | .literals                           |

|     | 6.4.15 | .lcomm symbol, length [, alignment] |

|     | 6.4.16 | .long exp $\{$ , exp $\}$           |

|     | 6.4.17 | section name [, "attributes"]       |

|     | 6.4.18 | .short $\exp \{, \exp \}$           |

|     | 6.4.19 | .text                               |

|     | 6.4.20 | .weak symbol [, symbol]             |

| 6.5 | Pseudo | -Instructions                       |

# CHAPTER 1

About this Document

This chapter would be organized with several sections as follows.

- Abstract

- $\bullet$  Purpose

- References

- Current status and anticipated changes

- Overview

## 1.1 Abstract

This manual defines the C-SKY V2 CPU Applications Binary Interface (ABI). The ABI consists of a serial of interfaces which the writer of compiler and assembler might follows, as composing tools for the C-SKY V2 CPU architecture. These standard covers several aspects of whole tool chain, varing from run-time to object formats, so as to make sure that different tool chain implementations of the C-SKY CPU shoule be compatible and interoperated.

Although compiler supportive routines are provided, this manual does not describe how to write C-SKY V2 CPU development tools, does not define the services provided by an operating system, and does not define a set of libraries. Those tasks must be performed by suppliers of tools, libraries, and operating systems.

# 1.2 Purpose

The standards only defined in this manual ensure that all components of development tool for C-SKY V2 CPU (do not include C-SKY V1 CPU) should be fully compatible with each other. Fully compatible tools could be interoperated, thus, making it is possible to select an optimal tool for each part in the chain instead of selecting an entire chain on the basis of overall performance. The Technology Center of Hangzhou C-SKY Microsystems Co., Ltd also provide a test suite to verify compliance with published standards.

It is sufficial for developer to follow by this standard. Concretely, the standards ensure that compatible libraries of binary components can be created and maintained. Such libraries make it is possible for developers to synthesize applications from binary components, and can make libraries of common services stored in on-chip ROM available to applications executing from off-chip ROM. With established standards, developer can build up libraries over time with the assurance of continued compatibility.

There are two goals required for implemented to conform to the standard.

- Use of interfaces that allow future optimizations for performance and energy.

- For example, when possible, registers are used to pass arguments, even though always using the stack might be easier. Small programs whose working sets fit into the registers are thus not forced to make unnecessary memory references to the stack just to satisfy the linkage convention.

- Use of interfaces that are compatible with legacy "C" code written for the C-SKY when possible.

- For example, whenever possible, C-SKY V2 CPU rules are used to build an argument list. This not only fits the C-SKY V2 CPU programmer's expectations, but easily supports

# 1.3 References

| GC++ABI            | http://www.codesourcery.com/    | Generic C++ ABI                  |

|--------------------|---------------------------------|----------------------------------|

|                    | cxx-abi/abi.html                |                                  |

| GDWARF             | http://dwarf.freestandards.org/ | DWARF 3.0, the generic debug     |

|                    | Dwarf3Std.php                   |                                  |

| GABI               | http://www.sco.com/developers/  | Generic ELF, 17 th December 2003 |

|                    | gabi/                           | draft.                           |

| GLSB               | http://www.linuxbase.org/spec/  | gLSB v1.2 Linux Standard Base    |

|                    | refspecs/                       |                                  |

| Open BSD           | http://www.openbsd.org/         | Open BSD standard                |

| C-SKY CPU ABI V1.0 | C-SKY CPU ABI Standards.pdf     |                                  |

Table 1.1: The references

# 1.4 Current status and anticipated changes

- 1. This manual has been released publicly. This manual is meant to be expandable.

- 2. Anticipated changes to this document include typographical corrections and clarifications.

- 3. Additional features about C++ ABI would be appended into this document to replect improvement in the future.

- 4. Supporting of PE object file format is anticipated to be added to this manual.

- 5. The Linux system interface for compiled application programs(The ABI for C-SKY V2.0 Linux)is anticipated to be added to this manual

- 6. TLS for Linux ABI, Thread Local Storage (TLS) is a class of own data (static storage), like stack, would be added.

# 1.5 Overview

Standards in this manual are intended to preclude creation of incompatible development tools for the C-SKY V2.0, by ensuring binary compatibility between:

- Object modules generated by different tool chains

- Object modules and the C-SKY V2.0 processor

- Object modules and source level debugging tools

Current definitions include the following types of standards.

# 1.5.1 Low-Level Run-Time Binary Interface Standards

- Processor specific binary interface, such as the instruction set, representation of primitive data types, and exception handling

- Function calling convention that the method of passing arguments and returning result on calling to another function arguments are passed and results are returned. This manual will specify how the argument should be passed by register or stack slot according to its type.

# 1.5.2 Object File Binary Interface Standards

- Header convention

- Section layout

- Symbol table format

- Relocation information format

- Debugging information format

## 1.5.3 Source-Level Standards

- C language, e.g. preprocessor predefines, in-line assembly, and name mapping.

- Assembly, e.g. the syntax and directives.

## 1.5.4 Library Standards

• Compiler assist libraries, including some library functions supporting operation on floating point and long long integer, for instance, addition of two integer of type long long, etc.

# 1.5.5 Change history

Table 1.2: Record of Change

| Revision | Date       | Changed by   | Description                                      |

|----------|------------|--------------|--------------------------------------------------|

| V2.0     | 2011-12-14 | LiChunQiang  | First public release used only for C-SKY V2 CPU  |

| V2.1     | 2018-04-13 | JianpingZeng | Second public release used only for C-SKY V2 CPU |

# Lower-level Binary interfaces

In order to served as a well documented index, this chapter would be splitted into following several different sections.

- Processor Architecture

- Function Calling Convention

- Runtime Debugging Support

## 2.1 Processor Architecture

C-SKY processor is a 32-bit high-performance and low-power embedded processor designed for embedded system or SoC environment. It adopts independently design of architecture and micro-achitecture with extensible instruction set, which owns great features, e.g. configurable hardware, re-synthesis, easily integration etc. Additionly, it is excellent in power management. It adopts several strategies to reduce power consumption including statically designed and dynamic power supply management, low voltage supply, entering low power mode and closing internal function modules. Now, C-SKY CPU instruction system has two versions:

#### • C-SKY V1

Any CPUs confirmed C-SKY V1.0 Instructions are always 16-bit and are aligned on a 2-byte boundary. There are two sub-serials, CK500 & CK600. The serial of CK500 include CK510, Ck520, CK510(ES), and CK600 include CK610, ck620 and ck610(ESM-F). CK510 is the first generation of C-SKY IP. Also CK610 is the second generation of C-SKY IP which is more efficient than CK510. CK520/CK620 adds OMFLIP, MAC, MTLO, MTHI, MFHI and MFLO instructions based on CK510/CK610 instruction set.

'E' means DSP enhancement, 'S' means SPM, 'M' means MMU, and '-F' means supporting of Float Point. Pelease consult the CK500 & CK600 Reference Manual to view description for detailed information.

## • C-SKY V2

The 2nd generation of instruction set of CK-CPU, which has more power and extensible instructions set than CK500 & CK600, even though second one is compatible with CK500 & CK600 in the level of assemble language. C-SKY V2.0 instruction set is the freely mixture of 32-bit and 16-bit instruction, and it's alignment boundary is two bytes.

## What's important is:

- Most of 16-bit instructions have been limited to only access 8 of partial general- purpose registers, r0-r7, known as the low registers. A few number of 16-bit instructions have the legal accessibility to the high registers, r8-r15.

- In the most of cases, operations should be accomplished by at least two 16-bit instructions so as to gain more efficiency.

You must note that the C-SKY V2.0 instruction sets are not freely exchangebale with V1.0. Conversely, available function provided by V2.0 is identical to V1.0 for most of applicatios. So that we strongly recommend that you should make sure you are aware of the generated result of specified application when you use them stimuleously. The two instruction sets differ in how instructions are encoded:

The standards defined in this manual ensure that all parts of development tools for C-SKY V2 CPU (do not include C-SKY V1 CPU) would be fully compatible.

# 2.1.1 Control Registers in C-SKY V2.0

The C-SKY ABI V2 defines an array of rules illustrating the developer should how to use the 32 general-purpose 32-bit registers of the C-SKY V2.0 processor. These registers are named  $r0\sim r31$  or  $a0\sim a6/t0\sim t10/l0\sim l10/gb/sp/lr$ . C-SKY V2.0 Co-processor 0 has up to 32 control registers. These registers are named cr0 through cr31. The control registers are shown in Table 2.1. These control registers can access with mtcr/mfcr instructions.

Register Use Convention Name Reg **Function** cr0Processor Status Register psr, cr0 cr1vbr,cr1 Vector Base Register Shadow Exception PSR cr2epsr,cr2 cr3fpsr,cr3 Shadow Fast Interrpt PSR Shadow Exception Program Counter cr4epc,cr4 Shadow Fast Interrupt PC cr5fpc,cr5 cr6ss0,cr6Supervisor Scratch Register Supervisor Sratch Register cr7ss1,cr7 Supervisor Scratch Regsiter cr8ss2,cr8cr9ss3,cr9 Supervisor Scratch Register Supervisor Scratch Register cr10ss4,cr10 cr11gcr,cr11 Global Control Register Global Status Register cr12gsr,cr2 cr13cpidr Product ID Register cr14cr14Rerserved cr15cr15Rerserved Rerserved cr16cr16Cache Flush Register cr17cfr cr18Cache Config Register  $\operatorname{ccr}$ Cachable and Access Popedom Register(MGU processor only) cr19 capr cr20Protected Area Config Register (MGU processor only) pacr Protected Area Select Register (MGU processor only) cr21prsr cr22-cr31 cr22-cr31Reserved

Table 2.1: C-SKY V2 Controls Register

The ABI does not mandate the semantics of the C-SKY Hardware Accelerator Interface (HAI) because these semantics vary between C-SKY implementations based on particular chips. C-SKY V2 provides instruction encodings to move, load, and store values for up to other 15 co-processors (except for co-processor 0).

# 2.1.2 Primary Data Type

The C-SKY processor works with the following raw data types:

- 1. unsigned byte of eight bits

- 2. unsigned halfword of 16 bits

- 3. unsigned word of 32 bits

- 4. signed byte of eight bits

- 5. signed halfword of 16 bits

- 6. signed word of 32 bits

As the listed above, the data size could be 8-bit bytes, 16-bit halfwords and 32-bit words. The mapping between these data types and the C language fundamental data type is shown in Table 2.2.

| Fundamental Data Types |            |       |                   |  |

|------------------------|------------|-------|-------------------|--|

| ANSI C                 | Size(byte) | Align | C-SKY             |  |

| char                   | 1          | 1     | unsigned byte     |  |

| unsigned char          | 1          | 1     | unsigned byte     |  |

| signed char            | 1          | 1     | signed byte       |  |

| short                  | 2          | 2     | signed halfword   |  |

| unsigned short         | 2          | 2     | unsigned halfword |  |

| signed short           | 2          | 2     | signed halfword   |  |

| long                   | 4          | 4     | signed word       |  |

| unsigned long          | 4          | 4     | unsigned word     |  |

| signed long            | 4          | 4     | signed word       |  |

| int                    | 4          | 4     | signed word       |  |

| unsigned int           | 4          | 4     | unsigned word     |  |

| signed int             | 4          | 4     | signed word       |  |

| enum                   | 4          | 4     | signed word       |  |

| pointer                | 4          | 4     | unsigned word     |  |

| long long              | 8          | 8     | signed word[2]    |  |

| unsigned long long     | 8          | 8     | unsigned word[2]  |  |

| float                  | 4          | 4     | unsigned word     |  |

| double                 | 8          | 8     | unsigned word[2]  |  |

| long double            | 8          | 8     | unsigned word[2]  |  |

Table 2.2: Mapping of C Fundamental Data Types to the C-SKY

Memory access to unsigned byte-sized data is directly supported through both ld.b (load byte) and st.b (store byte) instruction. Signed byte-sized access requires a sextb (sign extension) instruction after the ld.b. alternatively, memory access to signed byte-sized data can be directly supported through the ld.bs (load byte) and st.bs (store byte) instructions. Access to unsigned halfword-sized data is directly supported through the ld.h (load halfword) and st.h (store halfword) instructions. Signed halfword access requires a sexth (sign extension) instruction after the ld.h. In the other hand, memory access to signed halvword-sized data can be directly supported through the ld.hs (load byte) and st.hs (store byte) instructions. Memory access to word-sized data is supported through ld.w (load word) and st.w (store word) instruction. Also, ld.w suffices for both signed and unsigned word access because the operation sets all 32 bits of the loaded register.

| bit31          | Big e           | endian          | bit   | 0              |

|----------------|-----------------|-----------------|-------|----------------|

| Byte0          | Byte1           | Byte2           | Byte3 | address 0      |

| Byte4          | Byte5           | Byte6           | Byte7 | address 4      |

| Byte8          | Byte9           | ByteA           | ByteB | address 8      |

|                |                 |                 |       |                |

| bit31          | Little          | endian          | bit   | 0              |

| bit31<br>Byte3 | Little<br>Byte2 | endian<br>Byte1 | Byte0 | 0<br>address 0 |

|                |                 |                 |       | 1              |

Figure 2.1: Data layout in memory

Table 2.3: Data Layout in register

| SSSSSSSSSSS         | S Byte        |  |

|---------------------|---------------|--|

| 00000000000000      | Byte          |  |

| SSSSSS   S halfword |               |  |

| 0000000   Halfword  |               |  |

| Byte0   Byte1       | Byte2   Byte3 |  |

C-SKY V2 CPU supports standard two's complement data formats. The operand size for each instruction is either explicitly encoded in the instruction (load/store instructions) or implicitly defined by the instruction operation (index operations, byte extraction). Typically, instructions operate on all 32 bits of the source operand(s) and generate a 32-bit result.

C-SKY V2 CPU memory might be working in big endian or little endian byte ordering depending on the processor configuration (see Figure 2-1 Data Organization in Memory). When configurated with big endian mode (by default), the most significant byte (byte 0) of word 0 is located at address 0. For little endian mode, the most significant byte of word 0 is located at address 3. Any data of primitive type is always naturally aligned in memory, i.e., a long is 4-byte aligned, a short is 2-byte aligned.

Within registers, bits are numbered within a word starting with bit 31 as the most significant bit (see Figure 2-2 Data Organization in Registers). By convention, byte 0 of a register is the most significant byte regardless of Endian mode. This is only an issue when executing the xtrb[0-3] instructions.

The C-SKY processor currently does not support the long long int data type with 64-bit operations. However, compliant compilers must emulate the data type. The long long int data type, both signed and unsigned, is eight bytes in length and 4-byte aligned.

Requiring long long int support as part of the ABI insures that the feature will exist in all tool chains, so that application developers can depend on its existence. Because C-SKY processor can only hold a 32 bits data in a register, long long or double must be held in two registers(like r1,r2), and the most significant word of long long or double always is held in the upper register(like r2), the other word is held in the lower register(like r1) for big endian or little endian. when storing in memory, the most significant word of long long or double always is held in the upper address, the other word is held in the lower address for big endian or little endian. The C-SKY processor currently support floating point data with coprocessor FPU. Compliant compilers must support its use. The floating point format to be used is the IEEE standard for float and double data types. Supporting for the long double data type is optional but must conform to the IEEE standard format when provided. Alignments are specifically chosen to avoid the possibility of access faults in the middle of an instruction (with the exception of load/store multiple).

## 2.1.3 Composite Data Type

There is no two same leaf in the world, compound data types, such as array, structure, union, and bit fields, have different alignment characteristics. Arrays have the same alignment as their individual elements. Unions and structures have the most restrictive alignment of their members. A structure containing a char, a short, and an int must have 4-byte alignment to match the alignment of the int field. In addition, the size of a union or structure must be an integral multiple of its alignment. Padding must be applied to the end of a union or structure to make its size a multiple of the alignment. Members must be aligned within a union or structure according to their type; padding must be introduced between members as necessary to meet this alignment requirement. Bit fields cannot exceed 32 bits nor can they cross a word (32 bit) boundary. Bit fields of signed short and unsigned short type are further restricted to 16 bits in size and cannot cross 16-bit boundaries. Bit fields of signed char and unsigned char types are further restricted to eight bits in size and cannot cross 8-bit boundaries. Zero-width bit fields pad to the next 8, 16, or 32 bit boundary for char, short, and int types respectively. Outside of these restrictions, bit fields are packed together with no padding in between. Bit fields are assigned in big-endian order, i.e., the first bit field occupies the most significant bits

while subsequent fields occupy lesser bits. Unsigned bit fields range from 0 to 2–1 where "w" is the size in bits. Signed bit fields range from  $-2^{w-1}$  to  $2^{w-1}-1$ . Plain int bit fields are unsigned. Bit fields impose alignment restrictions on their enclosing structure or union. The fundamental type of the bit field (e.g., char, short, int) imposes an alignment on the entire structure. In the following example, the structure more has 4-byte alignment and will have size of four bytes because the fundamental type of the bit fields is int, which requires 4byte alignment. The second structure, less, requires only 1-byte alignment because that is the requirement of the fundamental type (char) used in that structure. The alignments are driven by the underlying type, not the width of the fields. These alignments are to be considered along with any other structure members. Struct careful requires 4-byte alignment; its bit fields only require 1-byte alignment, but the field fluffy requires 4-byte alignment.

```

struct more

{

int first : 3;

unsigned int second : 8;

};

struct less

{

unsigned char third : 3;

unsigned char fourth : 8;

};

struct careful

{

unsigned char third : 3;

unsigned char fourth : 8;

int fluffy;

};

```

each field of structure or union starts on the next possible suitably aligned boundary for their data type. For non-bit fields, this is a suitable byte alignment. Specially, bit field begin at the next available bit offset with the following exception: the first bit field after a non-bit field member will be allocated on the next available byte boundary. In the following example, the offset of the field "c" is one byte. The structure itself has 4-byte alignment and is four bytes in size because of the alignment restrictions introduced by using the "int" under-lying data type for the bit field.

```

struct s

{

int bf : 5;

char c;

};

```

This act behaves as same as the rules defined by UNIX System V Release 4 ABIs.

# 2.2 Function Calling Convention

## 2.2.1 Register Assignments

#### 2.2.1.1 General Registers

In Table 2.4, showing the required register mapping for function calls. Some registers, such as the stack pointer, have specific purposes, while others are used for local variables, or to transist function call arguments and return values.

Certain registers are bound to their purpose because specific instructions use them. For instance, subroutine call instructions write the return address into r15. The instructions used to save and restore registers on

entry and exit from a function use r14 as a base register, making it most appropriate for the stack pointer register.

Reference to "Argument Passing" and "Return Values" section for the detailed illustration of how arguments are passed or how the compiler handle the return value.

Register Use Convention Name Software Cross-Call Status Usage name Argument Word 1-2/Return Address Destroyed r0-r1 a0-a1 Argument Word 3-4 r2-r3 a2-a3 Destroyed r4-r11 10-17 Local Preserved r12-r13 t0-t1 Temporary registers used for expression Destroyed evaluation stack pointer r14Preserved spr15 lr link Preserved r16-r17 18-19 Local Preserved r18-r25 t2-t9 Temporary registers used for expression Destroyed evaluation r26 r26 Linker register Reserved r27 r27 Assembler register reserved Data section base address /GOT based Adr28 rdb/rgb reserved/Perserved dress for PIC rtbText section base address r29 reserved Handler Base address r30r30/svbr reserved r31 tlsTLS register reserved Program counter can't be accessed directly рс pc by instructions Multiply special register. Holds the most hi hi Destroyed significant 32 bits of multiply lo lo Multiply special register. Holds the least Destroyed significant 32 bits of multiply

Table 2.4: C-SKY V2.0 Register Assignment

## 2.2.1.2 Float Point Registers

The C-SKY V2.0 provides instruction encodings to move, load, and store values for up to 16 co-processors. Co-processor 1 adds  $16\ 32/64/128$ -bit floating-point general registers for single / double / SIMD double.

Floating-point data representation is that specified in IEEE Standard for Binary Floating-Point Arithmetic, ANSI/IEEE Standard 754-1985. Table 2.5 Registers describes the conventions for using the floating-point registers.

| Name     | Usage                          | Cross-Call status |

|----------|--------------------------------|-------------------|

| fr0      | Argument Word 1/Return Address | Destroyed         |

| fr1-fr3  | Argument Word 2-4              | Destroyed         |

| fr4-fr7  | Temporary registers            | Destroyed         |

| fr8-fr15 | Local registers                | Preserved         |

Table 2.5: Float point Registers

#### 2.2.1.3 Cross-Call Lifetimes

The 32 general-purpose registers are split between those preserved and those destroyed across function calls. This balances the need for callers to keep values in registers across calls against the need for simple leaf subroutines to perform operations without allocating stack space and saving registers. The preserved registers are called non-volatile registers. The registers that are destroyed are called volatile registers. Registers r4 through r7 are preserved because some 16-bit instructions can only access r0-r7 registers, so we can have a high performance and code density with 16-bit instructions.

The called subroutine can use any of the argument and scratch registers without concerning for restoring their values. Preserved registers must be saved before being used and restored before returning to the caller. While the called function is not specifically required to save and restore r15. On entry to functionm r15 usually contains the return address, so that it's value should be written into stack slot for making suring that the program can find the target address after callee is finished. The caller must preserve any essential data stored in argument and scratch registers. Data in these registers does not survive across function calls.

There is no register dedicated as a frame pointer. For non-alloca() functions, the frame pointer can always be expressed as an offset from the stack pointer. For alloca() functions and functions with very large frames, a frame pointer can be synthesized into one of the non-volatile registers.

Eliminating the dedicated frame pointer makes another register available for general use, with a corresponding improvement in generated code. This affects stack tracing for debugging. See 2.3 Runtime Debugging Support for additional information.

## 2.2.2 Stack Frame Layout

The stack pointer points to the bottom (low address) of the stack frame. Space at lower addresses than the stack pointer is considered invalid and may actually be unaddressable. The stack pointer value must always be a multiple of eight.

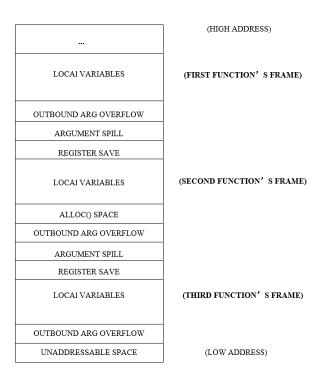

As the *Stack Frame Layouts* depicted, First() calls Second() which calls Third() shows typical stack frames for three functions, indicating the relative position of local variables, parameters, and return address. The outbound argument overflow must be located at the bottom (low address) of the frame. Any incoming argument spill generated for vararg and stdarg processing must be at the top (high address) of the frame. Space allocated by Alloca() must reside between the outbound argument overflow and local variable area.

The caller must store argument variables that do not fit in the argument registers in the outbound argument overflow area. If all outbound arguments fit in registers, this area is not required. A caller may allocate a succession of argument overflow space sufficient for the worst-case call, use portions of it as necessary, and not change the stack pointer between calls. The caller must reserve stack space for return variables that do not fit in the first two argument registers (e.g., structure returns). This return buffer area is typically adjecent to the local variables. Note that only in the function return structure value, this space would be allocated.

The caller may store the return address (r15) and the content of other local registers in the register save area upon entry to the called subroutine. If a called routine does not modify local variables (including r15), this area is not required.

Local variables that do not fit into the local registers are allocated in the Local Variable area of the stack. If there are no such variables, this area is not required. Beyond these requirements, a routine is free to manage its stack frame.

#### 2.2.2.1 Extending the Stack

Stack maintenance is the responsibility of system software. In some environments, it may be benefitial for compiler to probe the stack as they extend it in order to allow memory protection hardware to provide

Figure 2.2: Stack Frame Layouts

"guard pages".

## 2.2.3 Argument Passing

The C-SKY V2 CPU uses four registers (r0–r3) to pass the first four words of arguments from the caller to the called routine. If additional argument space is required, the caller is responsible for allocating this space on the stack. This space (if needed by a particular caller) is typically allocated upon entry to a subroutine, reused for each of the calls made from that subroutine that have more arguments than fit into the four registers used for subroutine calls, and deallocated only at the caller's exit point. All argument overflow allocation and deallocation is the responsibility of the caller.

At entry to a subroutine, the first word of any argument overflow can be found at the address contained in the stack pointer. Subsequent overflow words are located at successively larger addresses.

#### 2.2.3.1 Scalar Arguments

Arguments are passed using registers r0 through r3, with no more than one argument assigned per register. Argument values that are smaller than a 32-bit register occupy a full register.

In addition, small argument values are right justified and possibly extended within the register. Small signed arguments (e.g., shorts) are sign extended; small unsigned arguments (e.g., unsigned shorts) are zero extended, while other small values (e.g., structures of less than four bytes) are not extended, leaving the upper bits of the register undefined. The caller is responsible for sign and zero extensions. Small arguments that are passed via the argument overflow mechanism are placed in the overflow word with the same orientation they would have if passed in a register; a char is passed in the low-order byte of an overflow word. Such small overflow arguments need not be sign extended within the argument word as they would be if passed in a register. Arguments larger than a register must be assigned to multiple argument registers as long as

there are argument registers available. Arguments that would be aligned on 4-byte boundaries in memory (double, long double, long long, or structures or unions containing a double, long double or long long) can begin in any numbered register. Once all the argument registers are used, or if there are not enough registers left to hold a large argument, the argument and any subsequent arguments must be placed in the overflow area described above.

Large arguments can be split in register and in the overflow area when there are too few argument registers to hold the entire argument.

The caller is responsible for allocating argument overflow space and for deallocating any space needed for argument overflow. The only argument space that may be allocated or deallocated by the called routine is space used to place the register arguments in memory. This may be necessary for stdargs or structure parameters. Alignment is forced for atomic data types; fundamental data types are not split.

## 2.2.3.2 Structure Arguments

Structures passed as arguments can be partially or wholly passed through the argument registers. A structure argument may overflow onto the stack only when all argument registers are full. In these cases, the caller must adjust the stack pointer to allocate theoverflow area.

Structure arguments that are smaller than 32 bits have their value right justified within the argument register. The unused upper bits within the register are undefined.

Structure arguments larger than 32 bits are packed into consecutive registers. Structures that are not integral multiples of 32 bits in size have their final bits left justified within the appropriate register. This allows those bits to be stored with a 32-bit operation and be adjacent to the preceding portion of the structure.

# 2.2.4 Variable Arguments

The stdarg C macros provide with a mechanism to handle variable length argument lists. The caller might not know whether the called function handles variable arguments, so the called routine is responsible for handling the access to variable argument lists.

## 2.2.4.1 Spilling Register Arguments

Variable argument lists are most easily handled by spilling one or more of the register arguments so that they are adjacent to any overflow arguments that are on the stack at function entry.

The typical sequence should extend the stack several words, spill the argument registers after the last named argument into this space, and then proceed with the normal prologues to allocate a stack frame and save any non-volatile registers. The stdarg macros can use the address of the first stored argument register for the va\_start macro. The va\_arg macro advances this pointer by an amount appropriate to the size of the type specified.

## 2.2.4.2 Legacy Code Compatibility

The C-SKY V2 CPU linkage convention provides with a way for variable argument lists to be handled in a way that is compatible with legacy C code written for processors where the entire argument list is passed in memory.

The legacy behavior might wastes more instructions, stack slots, and memory references than required by strict interpretation of the ANSI C standards. Tool generators must provide with this legacy behavior as an option. It is not required as a default behavior.

To obtain compatibility, the called function must spill all the argument registers, rather than just those beyond the registers that hold the named arguments. This is more pessimistic than required for the stdarg definitions, but gain the most compatibility.

Spilling is triggered for functions that take the address of any of their arguments. This allows non-standard varargs code (C code that works on processors with all arguments passed in memory) to run on the C-SKY V2 CPU.

The spilled arguments are a snapshot of their values at the time the function is entered. This requirement does not force the compiler to generate code that keeps the "live" value of the parameters in memory. For example, the following would not be required to print out the value "4".

```

void func(int a, int b, int c, ...)

{

int *ip = 0;

use(c);

ip = &b;

ip++;

*ip = 4;

printf("c now has value %d\n", c);

}

```

The compiler is free to keep the value of c in diffirent location, either register or stack slot. The only requirement is to save a snapshot of the parameter passing registers (e.g., r0 through r3) during the function prologue.

## 2.2.5 Return Values

#### 2.2.5.1 Scalar Values

Subroutines return values in the argument registers. Return values smaller than 32 bits occupy a full register. These must be right justified and zero or sign extended to 32 bits before return (refer to "Scalar Arguments"). Return values of 32 bits or fewer are returned in register r0.

Return values between 33 and 64 bits are returned in the register pair r0/r1. The portion of the data that would reside at a lower address if stored in memory is in r0. For example, r0 would contain the most significant 32 bits of the long long data type.

Return values larger than eight bytes are treated as structure return values and are returned through memory. The return value is placed in a caller-supplied buffer. The buffer address is passed from the caller to the called routine as a hidden first argument in register r0.

### 2.2.5.2 Structure Values

Structures can be returned in one of two ways. Small structures (eight bytes or fewer) are returned in the register pair r0/r1. If the structure consists of four or fewer bytes, the value is returned in r0, right justified. This matches the way it would be justified when passed as an argument. If the structure consists of five to eight bytes, the first four bytes are returned in r0 and the trailing portion of the structure is returned left justified in r1.

This alignment is chosen to generate good code for code sequences such as

```

wom(..., bat(), ...)

```

where wom takes a structure argument of the same type returned by bat. The only work required is to perhaps change registers if the call to wom has the structure in some place other than r0/r1.

14

Structures larger than eight bytes are placed in a buffer provided by the caller. The caller must provide with a buffer with sufficient size. The buffer is typically allocated on the stack, in order to provide re-entrancy and to avoid any race conditions where a static buffer may be overwritten. The address of the buffer is passed to the called function as a hidden first argument and assigned in register r0. The normal arguments start in register r1 instead of in r0, restricted by as same constraints as fundamental data type.

The caller must provide this buffer for large structures even when the caller does not use the return value (e.g., the function was called to achieve a side-effect). The called routine can thus assume that the buffer pointer is valid and need not validate the pointer value passed in r0.

When r0 is used to pass a buffer address, the called routine must preserve the value passed through r0. The caller can thus assume that r0 is preserved when the buffer address of a large structure is passed in r0. This is similar to the way where streat and memory return their respective destination addresses.

In generaly, the temporary buffer, used for such structure returns, is immediately used as a source for a memcpy to a final destination. For example, the sequence

```

struct s {...}s, sfunc();

s = sfunc();

```

will often be compiled with sfunc returning into a temporary buffer, which is immediately copied into s. Although the caller must know the address of the temporary buffer so as to supply it for the called routine, the address need not be recalculated. In turn, the called routine can use the address to copy the results into the temporary buffer using memcpy, which returns the destination address (e.g., r0 has the desired value), or passes it to in-line code which uses r0 as a base register.

# 2.3 Runtime Debugging Support

It is one of the most difficult for C-SKY V2 CPU to trace stack. Tracing is complicated because the linkage convention does not mandate a frame pointer register and does not provide with any back-chain construct. This section describes rules for generating function prologues that can be easily decoded by a debugger to determine the size of a stack frame, the location of the return address, and the location of any saved non-volatile registers.

# 2.3.1 Function Prologues in C-SKY V2.0

Function prologues acquire stack space needed by the function to store local variables. This includes space the function uses to save non-volatile registers. Prologue instruction sequences can take a number of forms. A set of working assumptions about function prologues follows.

The function prologue is the only place in the function that acquires stack space, other than later calls to alloca().

The function prologue uses only the following classes of instructions.

```

subi sp, imm (Note that this might appear multiple times in a prologue)

subi sp, rx

push

st.w rx, (sp, disp)

mov rn, sp

```

This is optional support for traceback through alloca() using functions, and also marks the final instruction in the prologue.

The function prologue is organized roughly as:

- If stdarg, acquire space to store volatile registers; store volatile registers.

- Acquire space to store non-volatile registers.

- Store non-volatile registers that may be modified in this function.

- Acquire any additional stack space required. This space acquisition might be folded in with earlier ones if the total space allocated is no more than 32 bytes.

- If needed in this function, copy the stack pointer into one of the non-volatile registers to act as a frame pointer.

- Larger frames should allocate the register save space and then allocate the remainder of the required stack space rather than perform a single large stack acquisition. If the stack is acquired in a single allocation before the non-volatile registers are saved, then another base register is needed to reach the location for the stored registers. The prologue recognition code in the debugger does not recognize using alternate base registers to store the non-volatile registers as being part of the prologue.

This sequence allows the stack pointer to be modified several times.

# 2.3.2 Stack Tracing

Stack tracing for the C-SKY V2 CPU depends on the ability to determine the entry point for a function, given a PC value in that function. Since there are no unique prologue-only patterns in the instruction stream that can be identified by scanning backwards from the current PC. So a symbol table for the executable file must be present. The symbols need not be complete DWARF information.

Placing a specific byte pattern just before the prologue is not sufficient to identify the beginning of a function because the pattern can also appear within the body of the function as part of a literal table. In code-size sensitive environments, the extra space consumed by such a byte pattern is undesirable.

The stack tracing code iteratively performs the following:

- 1. Get the current PC.

- 2. Find the beginning of the containing function. Stop if this can't be determined.

- 3. Decode the prologue starting at the function's entry.

- 4. Determine the "top of frame" from the framesize information described in the prologue. This is either an adjustment to the stack pointer or a "pseudo-frame pointer" if the prologue ends with a frame pointer generating instruction.

- 5. Recover stored non-volatile registers based on the offsets described in the prologue. Repeat for the next frame.

High language Issures

This chapter would be divided into several sections to be illustrated as follows.

- ullet C preprocessor predefinitions

- Inline assembly syntax

- Name mapping

# 3.1 C preprocessor predefinitions

All C language compilers must predefine such symbol related to C-SKY CPU, \_\_CKCORE\_\_ , \_\_CSKY\_\_ , and \_\_csky\_\_ with the value "1" to indicate that the compiler targets the C-SKY V1.0 processor, and the value "2" to indicate that the compiler targets the C-SKY V2.0 processor. \_\_CSKYABI\_\_ , \_\_cskyabi\_\_ with the value "1" to indicate that the compiler targets the C-SKY ABI V1.0, and the value "2" to indicate that the compiler targets the C-SKY ABI V2.0.

When big endian was configured in target machine, all C language compilers must predefine the symbol \_\_BIG\_ENDIAN\_\_ , or symbol \_\_LITTLE\_ENDIAN\_\_ .

# 3.2 Inline assembly syntax

## 3.2.1 Overview

When developing for the special applications or taking the advantage of recently advanced instructions which temporally can't be generated by compiler, it is needed to cast our sight to the assembly language. With assisttant of assembly code, developer can operate the lower level registers or instructions. This is machenism named of *Inline Assembly* provided by GNU extension to normal C standard. Also, C-SKY compiler supports this benefitial feature based on GCC(GNU compiler collection).

Inline assembly is important primarily because of its ability to operate and make its output visible on C variables. Because of this capability, "asm" works as an interface between the assembly instructions and the "C" program that contains it.

## 3.2.2 Basic usage

format of basic inline assembly is very much straight forward. Its basic form is,

```

asm("assembly");

```

Example for C-SKY V2.0 is as follow.

You might have noticed that here I've used asm and \_\_asm\_\_. Both are valid. We can use \_\_asm\_\_ if the keyword asm conflicts with something in our program. If we have more than one instructions, we write one per line in double quotes, and also suffix a 'n' and 't' to the instruction, since compiler sends each instruction as a string to assembler and by using the newline/tab we send correctly formatted lines to the assembler. The exmaple used for illustrating this as follows.

If in our code we touch (ie, change the contents) some registers and return from asm without fixing those changes, something bad is going to happen. This is because compiler have no idea about the changes in the register contents and this leads us to trouble, especially when compiler makes some optimizations. It will suppose that some register contains the value of some variable that we might have changed without informing compiler, and it continues like nothing happened. What we can do is either use those instructions having no side effects or fix things when we quit or wait for something to crash. This is where we want some extended functionality. Extended asm provides us with that functionality.

## 3.2.3 Extended asm

In basic inline assembly, we had only instructions. In extended assembly, we can also specify the operands. It allows us to specify the input registers, output registers and a list of clobbered registers. It is not mandatory to specify the registers to use, we can leave that head ache to compiler and that probably fit into compiler's optimization scheme better. Anyway the basic format is.

The assembler template consists of assembly instructions. Each operand is described by an operand-constraint string followed by the C expression in parentheses. A colon separates the assembler template from the first output operand and another separates the last output operand from the first input, if any. Commas separate the operands within each group. The total number of operands is limited to ten or to the maximum number of operands in any instruction pattern in the machine description, whichever is greater.

If there are no output operands but there are input operands, you must place two succensive colons as the placeholder at where the output operands would go. For instance,

```

asm ("cmpei %0, 0\n\t"

"bt 1\n\t"

"stw %0, (%1, 0)"

"1:\n\t"

: /* no output registers */

: "r" (count), "r"(dest)

: "memory"

);

```

The above inline fills if :math: count!=0, store count into the memory which dest point to. It also inform compiler the contents of memory is changed. The following example will be served as role for expositing it more clearer.

```

int a=10, b;

asm ("mov r1, %1

mov %0, r1"

:"=r"(b) /* output */

:"r"(a) /* input */

:"r1" /* clobbered register */

);

```

Here what we did is taking the value of 'a' from 'b through using assembly instructions. Some interesting points are as follows.

- "b" is the output operand, referred to by %0 and "a" is the input operand, referred to by %1.

- "r" is a constraint on the operands. We'll see constraints in detail later. For the time being, "r" says to COMPILER to use any register for storing the operands. output operand constraint should have a constraint modifier "=". And this modifier says that it is the output operand and is write-only.

- There are two %'s prefixed to the register name. This helps COMPILER to distinguish between the operands and registers. operands have a single % as prefix.

- The clobbered register r1 after the third colon tells compiler that the value of r1 would to be modified inside "asm", so compiler shouldn't use this register to store any other value.

When the execution of "asm" is complete, "b" will reflect the updated value, as it is specified as an output operand. In other words, the change of "b" inside "asm" is supposed to be reflected outside the "asm".

# 3.2.3.1 Assembler Template

This section will uses some detailed description to explain the inline assembly grammar, e.g. either each instruction in inline assembly or all instructions respectively enclosed by double quotes. Also, each instruction should end with a delimiter, for instance, newline(n) or semicolon(;), 'n' may be followed by a tab(t). Operands corresponding to the C expressions are represented by %0, %1 ... etc.

## **3.2.3.2 Operands**

C expressions serve as a role for giving operands for the assembly instructions inside "asm". Each operand is written as first an operand constraint in double quotes. For output operands, there'll be a constraint modifier also within the quotes and then follows the C expression which stands for the operand.

"constraint" (C expression) is the general form. For output operands an additional modifier will be there. Constraints are primarily used to decide the address mode for operands. They are also used for specifying how the registers would be used.

If there are more than one operands, a comma should be introduced to separate them.

In the assembler template, each operand is referenced by number. We might use following rule to number all operands (including input operands and output operands). By assuming there are n operands, then the number of each output operand will be numbered as zero with step 1 in ascending order, and the last input operand is numbered as n-1.

Unlike input operands are not restricted, output operand expressions must be values. They may be expressions. The extended asm feature is usually used for machine instructions which the compiler itself does not know as existing;-). If the output expression cannot be directly addressed (for example, it is a bit-field), our constraint must allow a register. In that case, compiler will use the register as the output of the asm, and then store that register contents into the output.

As stated above, ordinary output operands must be write-only; compiler will assume that the values in these operands before the instruction are dead and need not be generated. Extended asm also supports input-output or read-write operands.

So now we can concentrate on some examples. We want to add a number by 5. For that we use the instruction add.

```

asm ("mov %0, %1\n\t"

"cmplt %0, %0\n\t"

"addc %0, 5"

: "=r" (five_times_x)

: "r" (x)

);

```

Here our input is in 'x'. We didn't specify which register to be used. compiler will choose some register for input, one for output and does what we desired. If we want the input and output to reside in the same register, we can tell compiler how to do so. Here we use those types of read-write operands. By specifying proper constraints, here we do it.

```

asm ("cmplt %0, %0\n\t"

"addc %0, 5"

: "=r" (five_times_x)

: "0" (x)

);

```

Now the input and output operands are reside in the same register. But we don't know which register.

In all the two examples above, we didn't put any register to the clobber list. why? In the first two examples, COMPILER decides the registers and it knows what changes happen.

#### 3.2.3.3 Clobber List

Some instructions clobber some hardware registers. We have to list those registers in the clobber-list, ie the field after the third ':' in the asm function. This is to inform compiler that we will use and modify them ourselves. So compiler will not assume that the values it loads into these registers will be valid. We shouldn't list the input and output registers in this list. Because, compiler knows that "asm" uses them (because they are specified explicitly as constraints). If the instructions use any other registers, implicitly or explicitly (and the registers are not present either in input or in the output constraint list), then those registers have to be specified in the clobbered list.

If our instruction can alter the condition code register, we have to add "cc" to the list of clobbered registers.

If our instruction modifies memory in an unpredictable fashion, add "memory" to the list of clobbered registers. This will cause compiler to not keep memory values cached in registers across the assembler instruction. We also have to add the volatile keyword if the memory affected is not listed in the inputs or outputs of the asm.

We can read and write the clobbered registers as many times as we like. Consider the example of multiple instructions in a template; it assumes the subroutine \_foo accepts arguments in registers r1 and r2.

```

asm ("movl r2, %0 \n\t

movl r3, %1 \n\t

jsri _foo"

: /* no outputs */

: "g" (from), "g" (to)

: "r2", "r3"

);

```

#### 3.2.3.4 Volatile

If you are familiar with kernel sources or some beautiful code like that, you must have seen many functions declared as volatile or \_\_\_volatile\_\_ which follows an asm or \_\_\_asm\_\_\_.

If our assembly statement must execute where we put it, (i.e. must not be moved out of a loop as an optimization), putting the keyword volatile after asm and before the ()'s. So as to keep it from moving, deleting and all, we declare it as.

```

asm volatile ( ... : ... : ...);

```

Use \_\_\_volatile\_\_ when we have to be very much careful.

If our assembly is just for doing some calculations and doesn't have any side effects, it's better not to use the keyword volatile. Avoiding it helps compiler in optimizing the code and making it more beautiful.

In the section Some Useful Recipes, there are many examples for inline asm functions. There we can see the clobber-list in details.

#### 3.2.3.5 Constraints

Constraints can say whether an operand may be in a register; whether the operand can be a memory reference, and which kinds of address; whether the operand may be an immediate constant, and which possible values (ie range of values) it may have.... etc.

There are a number of constraints in which few parts are used frequently. We'll have a look at those constraints.

1. Register operand constraint

When operands are specified using this constraint, they get stored in General Purpose Registers(GPR). Take the following as an example:

```

asm ("mov %0, %1\n"

:"=r"(myval)

: "=r"(inval));

```

Here, the variable myval is kept in a register, and the value in inval is copied onto that register. When the "r" constraint is specified, compiler may keep the variable in any of the available GPRs. To specify the register, you must directly specify the register name via using specific register constraints. They are:

For example:

## 2. Memory opernad contraint(m)

When the operands are preversed in the memory, any operations operated on them will occur directly in the memory location, as opposed to register constraints, which first store the value into a register to be modified and then write it back to the stack slot. But register constraints are usually used only when it is absolutely necessary for them to significantly speed up the process. Memory constraints can be used most efficiently in cases where a C variable needs to be updated inside "asm" and you really don't want to use a register to hold its value. For example, the value of input is stored in the memory location(loc):

## 3. Matching constraints

In some cases, a single variable may serve as both the input and the output operand. Such cases may be specified in "asm" by using corresponding constraints.

```

asm ("inct %0" :"=a"(var):"0"(var));

```

This constraint can be used on following scenario:

- In cases where input is read from a variable or the variable is modified and modification is written back to the same variable.

- In cases where separate instances of input and output operands are not necessary.

- Using of corresponding of constraints would have significant impact on efficient use of available registers.

- By using constraints, for more precise control over the effects of constraints, compiler will provides us with constraint modifiers. Mostly used constraint modifiers are listed as below.

- "=" means that this operand is write-only for this instruction. But, note that previous value is discarded and replaced by output data.

- "&" means that this operand is an early clobber operand, which is modified before the instruction is finished using the input operands. Therefore, this operand may not lie in a register that is used as an input operand or as part of any memory address. An input operand can be tied to an early clobber operand if its only use it as an input before the early result is broken.

# 3.2.4 Examples

• addition of two integer

The '=' sign indicates the output register.

In the output field, "=m" says that my\_var is an output operand and resides in memory. Similarly, "ir" says that, my\_int is integral and should reside in some register (recall the table we saw above). No registers are in the clobber list.

• Memory access

```

int main(int argc, char **argv)

{

int i;

char kk[10]

char ch;

__asm__ __volatile__ ("ldw %0, %1"

: "=r"(i)

: "m"(argc));

__asm__ __volatile__ ("stw %1, %0"

: "=o"(kk)

: "r"(i));

__asm__ __volatile__ ("stw %0, %1"

: "V"(argc));

__asm__ __volatile__ ("stw %1, %0"

: "=m"(kk[5])

: "r"(ch));

return 0;

```

• Linux System Calls

ON Linux platform, system calls are implemented using inline assembly. All the system calls are written as macros. For example, a system call with 1 arguments is defined as a macro as shown below.

Whenever a system call with 1 arguments occurs, the macro shown above is used for executing the specified function call. After call finishing, the syscall number is placed in r1, then each parameters in r2. And finally "trap 0" is the instruction which makes the system call work. The return value can be collected from r2.

#### Note

"\_\_errno\_location()" is a function call, and will return the result in r2, and function call for CKCORE will clobber r1 - r7, but "register long \_\_res \_\_asm\_\_("r2")" use "r2" also, so there

is a bug in the above example, It must be:

```

{

long __error = __res;

*__errno_location () = -__error;

__res = -1;

}

```

# 3.3 Name mapping

Externally visibility names a specified name in the C language must be mapped through to assembly language without change. We will use following example to illustrate this point.

```

void testfunc() { return;}

```

it will generates assembly code similar to the following fragment.

```

testfunc:

rts

```

# CHAPTER 4

ELF file format

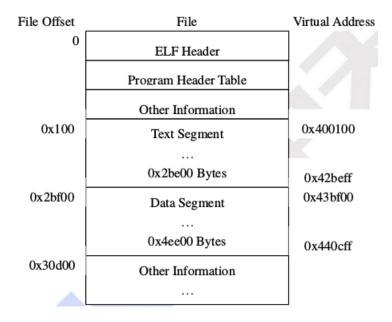

C-SKY V2 CPU tools use ELF object file formats(1.2 version) and DWARF 2.0 debugging information formats, as described in System V Application Binary Interface, from The Santa Cruz Operation, Inc. ELF and DWARF provide a suitable basis for representing the information needed for embedded applications. This section describes particular fields related to the ELF and DWARF formats that differ from the basic standards for those format.

This chapter will introduces several sections to exposite the ELF file format in detail.

- ELF Header

- Section Layout

- Symbol Table Format

- Relocation Information Format

- Program Loading

- Dynamic Linking

- PIC Examples

- Debugging Information Format

## 4.1 ELF Header

## • e\_machine

The e\_machine field of the ELF header contains the decimal value 39 (hexadecimal 0x27) which is named EM\_CSKY.

## • e\_ident

For file identification in e ident[] must be the values listed in Table 4.1.

Table 4.1: C-SKY e\_Ident Fields

| C-SKY e_Ident Fields |              |    |                                                     |

|----------------------|--------------|----|-----------------------------------------------------|

| eident[EICLASS]      | ELFCLASS32   |    | For all 32 bit implementations                      |

| eident[EIDATA]       | ELFDATA2LSB  | or | The choice will be governed by the default data or- |

|                      | ELFDATA2M SB |    | der in the execution evironment. ELFDATALSB:        |

|                      |              |    | Little Endian ELFDATA2MSB: Big Endian               |

## $\bullet$ e\_flags

In ABI v0.1, the ELF header e\_flags member contains zero, because the C-SKY processor family defines no flags at that time. Now e\_flags are shown in Table 4.2. Undesignated bits are reserved to future revisions of this specification.

Table 4.2: C-SKY-Specified e\_flags

| Name              | Mask                      |            | Value-Meaning                                                                                                                                                                                                                                                                                                                                 |

|-------------------|---------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EF_CSKY_ABIMASK   | 0xF0000000                |            | The integer value formed by these 8 bits identify extensions to the C-SKY A BI V0.1; In ABI V0.1, the ELF header e_flags member contains zero, because the C-SKY processor family defines no flags at that time; values > 0 indicates the object file or executbale contains program text using newer version of CSKY-ABI than C-SKY ABI V0.1 |

|                   |                           |            | 0b0000: V0.1<br>0b0001: V1.0                                                                                                                                                                                                                                                                                                                  |

|                   |                           |            | 0b0010: V2.0                                                                                                                                                                                                                                                                                                                                  |

|                   |                           |            |                                                                                                                                                                                                                                                                                                                                               |

| O+1 : f +:        | 00EEE0000                 |            | 041 : f                                                                                                                                                                                                                                                                                                                                       |

| Other information | 0x0FFF0000<br>EF_CSKY_PIC | 0x00010000 | Other information This bit is asserted when target file                                                                                                                                                                                                                                                                                       |

|                   | LI _OSKI_I IO             | 0.00010000 | contains posi tion independent code                                                                                                                                                                                                                                                                                                           |

|                   |                           |            | that can be relocated in memory                                                                                                                                                                                                                                                                                                               |

|                   | EF_CSKY_CPIC              | 0x00020000 | This bit is asserted when target file contains code that follows standard calling convention for calling PIC. It's not necessarilly position independent for object code. The EF_CSKY_PIC and EF_CSKY_CPIC flag can only be used exclusively.                                                                                                 |

|                   | Reserved                  | 0x0FFC0000 | Reserved                                                                                                                                                                                                                                                                                                                                      |

| EF_CSKY_PROCESSOR | 0x0000FFFF                |            | This integer consists of 8 bits, which used for identifing the instruction set version as follows.  (1<<0): CK510 (1<<1): CK610 (1<<2): CK801 (1<<3): CK810 (1<<14): DSP V1.0 (1<<15): MAC set                                                                                                                                                |

# 4.2 Section Layout

# 4.2.1 Section Alignment

The object generator (compiler or assembler) supplyes alignment information for the linker. The default alignment is eight bytes. Object producers must ensure that generated objects specify required alignment.

For example, an object file must reflect the fact that four-byte alignment is required in the data section.

#### 4.2.2 Section Attributs

Table 4.3 defines section attributes that are available for C-SKY V2 CPU tools. These attributes are additions to the ELF standard flags shown in Table 4.4.

Table 4.3: CKCORE Section Attribute Flags

| CKCORE Section Attribute Flags |            |  |  |

|--------------------------------|------------|--|--|

| Name                           | Value      |  |  |

| SHF_CKCORE_NOREAD              | 0x80000000 |  |  |

The SHF\_CKCORE\_NOREAD attribute allows the specification of code that is executable but not readable. Plain ELF assumes that all segments have read attributes, which is why there is no read permission attribute in the ELF attribute list. In embedded applications, "execute-only" sections that allow hiding the implementation are often desirable.

Table 4.4: ELF Section Attribute Flags

| ELF Section Attribute Flags |            |  |  |

|-----------------------------|------------|--|--|

| Name   Value                |            |  |  |

| SHF_WRITE                   | 0x00000001 |  |  |

| SHF_ALLOC                   | 0x00000002 |  |  |

| SHF_EXECINSTR               | 0x00000004 |  |  |

# 4.2.3 Special Sections

Various sections hold program and control information. Table 4.4 shows sections used by the system, the indicated types, and attributes. These are additional extensions to ELF standards shown in Table 4.5. The ELF standard reserves section names beginning with a period ("."), but applications may use those sections if their existing meanings are satisfactory.

C-SKY currently support PIC technique, when compiling PIC, the link editor will create .got and .plt sections, see " Global Offset Table " and " Procedure Linkage Table ".

Table 4.5: C-SKY V2 CPU Tools Special Sections

| C-SKY Section names for PIC |              |                         |  |  |

|-----------------------------|--------------|-------------------------|--|--|

| Name                        | Type         | Attributs               |  |  |

| .got                        | SHT_PROGBITS | SHF_ALLOC+SHF_WRITE     |  |  |

| .plt                        | SHT_PROGBITS | SHF_ALLOC+SHF_EXECINSTR |  |  |

## Note